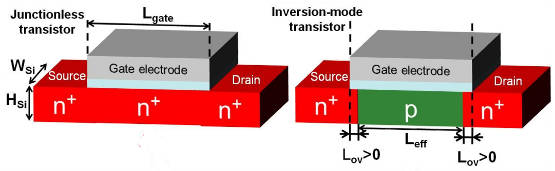

The junctionless transistor (JLT) is a multi-gate FET with no PN nor N+N or P+P junctions. The device is basically a resistor in which the mobile carrier density can be modulated by the gate. Genuine Toshiba 2SK30A JFET. Low Noise Silicon N-channel Junction Field Effect Transistor. American christianity chartonline lutheran bible study. Sweden, Singapore, South Korea, Singapore, Vietnam, Great Britain & Canada. Source and drain end 1–13. The junctionless FET’s offers diverse benefits over conventional FET’s also. It offers a facile way for fabricating the device and offers lower vul-nerability to short channel effects (SCE’s) 7. There is no inversion mode in the operation of junctionless FET’s.

Standard Dataset

- Citation Author(s):

- Cheng-Kuei Lee, Sen Yin, Jin-Yu Zhang, Zuo-Chang Ye,Yan Wang nad Zhi-ping Yu

- Submitted by:

- Sen Yin

- Last updated:

- Thu, 11/08/2018 - 10:34

- DOI:

- 10.21227/m6xf-3898

- License:

Abstract

This research examined the electrical characteristicsof a conventional junctionless silicon-on-insulator (SOI-JL) and aSOI hybrid P/N fin channel JL thin film transistor (SOI-H-JL)using a simulation with gate lengths from 60 nm to 10 nm. Theinterface location of the SOI-H-JL has a depletion region of aparallel channel, which influences the effective thickness of thechannel. The threshold voltage can be adjusted by changing theconcentration of the substrate. Better electrical characteristicsand higher transconductance can be obtained under the shortchannel when compared with the conventional SOI-JL. Althoughthe hybrid structure has better electrical characteristics, thelarger gate capacitance results in the delay time excessively longas a defect, which can be improved by thickening the raisedsource/drain area. The circuit performance is evaluated bybuilding up an inverter using aforementioned devices.

This research examined the electrical characteristicsof a conventional junctionless silicon-on-insulator (SOI-JL) and aSOI hybrid P/N fin channel JL thin film transistor (SOI-H-JL)using a simulation with gate lengths from 60 nm to 10 nm. Theinterface location of the SOI-H-JL has a depletion region of aparallel channel, which influences the effective thickness of thechannel. The threshold voltage can be adjusted by changing theconcentration of the substrate. Better electrical characteristicsand higher transconductance can be obtained under the shortchannel when compared with the conventional SOI-JL. Althoughthe hybrid structure has better electrical characteristics, thelarger gate capacitance results in the delay time excessively longas a defect, which can be improved by thickening the raisedsource/drain area. The circuit performance is evaluated bybuilding up an inverter using aforementioned devices.

Documentation

QUESTIONS?

How to Access this Dataset

This dataset requires an IEEE DataPort Subscription. Subscriptions are available for free for a limited time.

doi = {10.21227/m6xf-3898},

url = {https://dx.doi.org/10.21227/m6xf-3898},

author = {Cheng-Kuei Lee; Sen Yin; Jin-Yu Zhang; Zuo-Chang Ye;Yan Wang nad Zhi-ping Yu },

publisher = {IEEE Dataport},

title = {An Investigation of the Scalability of a 3D Stacked Hybrid P/N Layer and Vertical Gate SOI Junctionless FET},

year = {2018} }

T1 - An Investigation of the Scalability of a 3D Stacked Hybrid P/N Layer and Vertical Gate SOI Junctionless FET

AU - Cheng-Kuei Lee; Sen Yin; Jin-Yu Zhang; Zuo-Chang Ye;Yan Wang nad Zhi-ping Yu

PY - 2018

PB - IEEE Dataport

UR - 10.21227/m6xf-3898

ER -

Embed this dataset on another website

Copy and paste the HTML code below to embed your dataset:

Share via email or social media

Click the buttons below:

Share a link to this dataset

Junctionless Fet

Permalink: http://ieee-dataport.org/documents/investigation-scalability-3d-stacked-hybrid-pn-layer-and-vertical-gate-soi-junctionless

DOI Link: https://dx.doi.org/10.21227/m6xf-3898 44 pdf previewdialectical behavioral training.

Junctionless Tunnel Fet

Short Link: http://ieee-dataport.org/1082

Junctionless Tunnel Fet

View AWS Security Credentials

How to use Access Files on AWS